#### Louisiana State University

### LSU Scholarly Repository

LSU Doctoral Dissertations

**Graduate School**

11-6-2017

## Modeling of Thermally Aware Carbon Nanotube and Graphene Based Post CMOS VLSI Interconnect

K M Mohsin

Louisiana State University and Agricultural and Mechanical College

Follow this and additional works at: https://repository.lsu.edu/gradschool\_dissertations

Part of the Electrical and Electronics Commons, Electronic Devices and Semiconductor Manufacturing Commons, and the Nanotechnology Fabrication Commons

#### **Recommended Citation**

Mohsin, K M, "Modeling of Thermally Aware Carbon Nanotube and Graphene Based Post CMOS VLSI Interconnect" (2017). *LSU Doctoral Dissertations*. 4168.

https://repository.lsu.edu/gradschool\_dissertations/4168

This Dissertation is brought to you for free and open access by the Graduate School at LSU Scholarly Repository. It has been accepted for inclusion in LSU Doctoral Dissertations by an authorized graduate school editor of LSU Scholarly Repository. For more information, please contactgradetd@lsu.edu.

## MODELING OF THERMALLY AWARE CARBON NANOTUBE AND GRAPHENE BASED POST CMOS VLSI INTERCONNECT

#### A Dissertation

Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

The Division of Electrical and Computer Engineering

by

K M Mohsin

M.S., Louisiana State University, Baton Rouge, 2017

B.S., Bangladesh University of Engineering and Technology, Bangladesh, 2011

December 2017

To my parents, for all their life long sacrifices to prepare me for this long journey...

#### **ACKNOWLEDGMENTS**

I like to take this opportunity to thank my advisor Dr. Ashok Srivastava for his untiring efforts in training me as a Ph. D. student. His timely reminder, micro-management along with relentless efforts towards my research made it easier for this great achievement. Beyond research I learned from him how to steer energy, motivation and courage to stand up for the right cause. I am grateful to him for his care a guidance which is a key to this journey of learning.

I am thankful to Dr. Ajmera for his efforts in corrections and insightful suggestion towards establishing this dissertation. I also like to thank Dr. Dowling and Dr. Pullin for their motivations towards learning Physics which eventually helped me to have a minor degree in Physics. I am thankful to Dr. Vaidy, Dr. Nguyen for their efforts as graduate committee members.

I am thankful to Dr. Ashwani K. Sharma and Mr. Clay Mayberry of US Air Force Research Laboratory, Kirtland Air Force Base, New Mexico, for their support and encouragement for the research carried out in this dissertation.

I would also like to thank Dr. Fahad, Dr. Khan for being great co-worker, co-author. I also like to thank Xinlu, Zhou Zhou, Shilpa and Murad for their various supports towards this dissertation.

## TABLE OF CONTENTS

| ACKNOWLEDGMENTS                                              | iii |

|--------------------------------------------------------------|-----|

| LIST OF TABLES                                               | vi  |

| LIST OF FIGURES                                              | vii |

| ABSTRACT                                                     | X   |

| CHAPTER 1 INTRODUCTION                                       | 1   |

| 1.1. Present Technology and Its Limitations                  |     |

| 1.2. ALTERNATIVE APPROACHES                                  |     |

| 1.3. Organization                                            |     |

| CHAPTER 2 ELECRTRO-THERMAL TRANSPORT OF CNT BASED VLSI       |     |

| INTERCONNECT                                                 | 13  |

| 2.1. Introduction                                            | 13  |

| 2.2. ELECTRICAL PROPERTIES OF CNTS                           | 15  |

| 2.3. THERMAL PROPERTIES                                      | 31  |

| 2.4. ELECTROTHERMAL COUPLED EQUATIONS                        |     |

| 2.5. TEMPERATURE PROFILE INSIDE THE INTERCONNECT             |     |

| 2.6. EFFECT OF INTERLAYER DIELECTRIC                         |     |

| 2.7. HIGH FREQUENCY PERFORMANCES IN TERMS OF S-PARAMETERS    |     |

| 2.8. Conclusion                                              | 70  |

| CHAPTER 3 MATERIAL SIMULATION WITH DENSITY FUNCTIONAL THEORY | 72  |

| 3.1. Introduction                                            | 72  |

| 3.2. HISTORY OF DFT                                          | 73  |

| 3.3. DFT AS A THEORY                                         |     |

| CHAPTER 4 GRAPHENE/COPPER HYBRID INTERCONNECT: RESISTIVITY   | 90  |

| 4.1. Introduction.                                           | 90  |

| 4.2. SIMULATION METHOD                                       | 93  |

| 4.3. RESULTS AND DISCUSSION                                  | 98  |

| 4.4. Conclusion                                              |     |

| CHAPTER 5 GRAPHENE/COPPER HYBRID INTERCONNECT: CAPACITANCE   | 115 |

| 5.1. Introduction                                            | 115 |

| 5.2. COMPUTATIONAL MODEL AND METHOD                          |     |

| 5.3. CALCULATION OF QUANTUM CAPACITANCE                      |     |

| 5.4. RESULTS AND DISCUSSION                                  |     |

| 5.5. QUANTUM CAPACITANCE MODELING:                           |     |

| 5.6. CONCLUSION                                              |     |

| CHAPTER 6 APPLICATION DEMONSTRATION IN HYBRID CMOS IC        | 133 |

| 6.1. Introduction                                            |     |

| 6.2 Circuit                                                  | 133 |

| 6.3. Interconnect parameters                    | 135 |

|-------------------------------------------------|-----|

| 6.4. DELAY ANALYSIS                             | 138 |

| 6.5. CONCLUSION                                 | 155 |

| CHAPTER 7 CONCLUSION                            | 157 |

| REFERENCES                                      | 159 |

| APPENDIX-A PARTIAL LIST OF SYMBOLS AND ACRONYMS | 171 |

| APPENDIX-B CODES                                | 174 |

| APPENDIX-C MATLAB CODE FOR FDTD TECHNIUQE       | 183 |

| VITA                                            | 184 |

## LIST OF TABLES

| Table 2.1: Thermoelectric properties of Cu, SWCNT and MWCNT                     | 14  |

|---------------------------------------------------------------------------------|-----|

| Table 2.2: Temperatures and equivalent resistances of SWCNT bundle interconnect | 46  |

| Table 2.3: Comparison with earlier works                                        | 63  |

| Table 5.1: Model parameters for different sizes of G/Cu                         | 129 |

| Table 6.1: NMOS model parameters                                                | 135 |

| Table 6.2: PMOS model parameters                                                | 135 |

| Table 6.3: Resistivity of Cu                                                    | 136 |

| Table 6.4: Interconnect parameters for various materials                        | 137 |

| Table 6.5: Model of voltage pulse source for FDTD study.                        | 146 |

| Table 6.6: Delay for different interconnect materials at 10 GHz                 | 150 |

| Table 6.7: Energy dissipated in interconnects                                   | 154 |

| Table 6.8: Energy delay product of various interconnects at 10 GHz.             | 155 |

## LIST OF FIGURES

| Figure 1.1: Cu/low-k interconnect technology                                                                                                                                                                                                                                | 3  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2: Current interconnect (Cu/low-k) process technology                                                                                                                                                                                                              | 6  |

| Figure 1.3: Increasing line resistance of Cu-low/k interconnect in scaled technology nodes                                                                                                                                                                                  | 7  |

| Figure 1.4: Comparison of transistor gate delay with interconnect's RC delay                                                                                                                                                                                                | 9  |

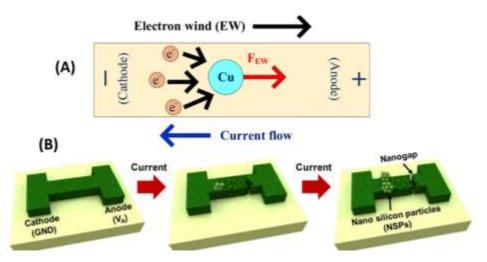

| Figure 1.5: (A) Electromigration phenomena (B) Nanogap formation due to electromigration                                                                                                                                                                                    | 10 |

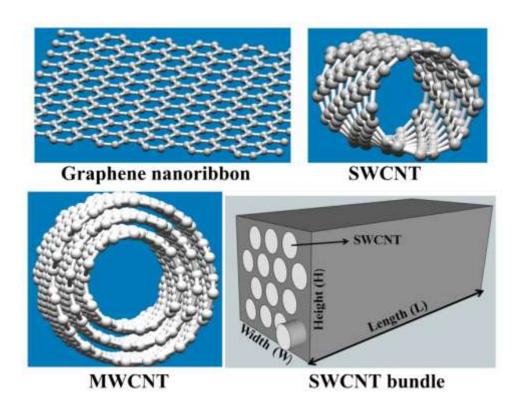

| Figure 2.1: Different carbon-based nanomaterials.                                                                                                                                                                                                                           | 16 |

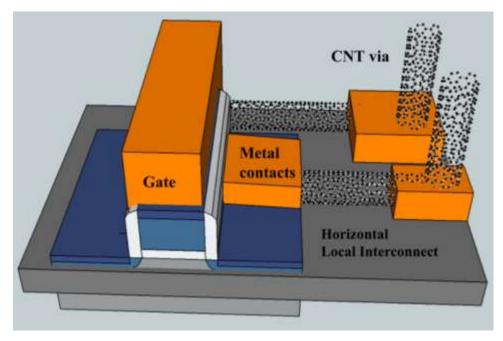

| Figure 2.2: SWCNT based VLSI interconnects.                                                                                                                                                                                                                                 | 18 |

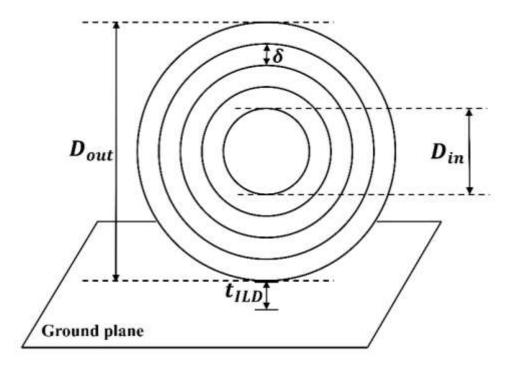

| Figure 2.3: Concentric circles showing MWCNT shells with the ground plane.                                                                                                                                                                                                  | 22 |

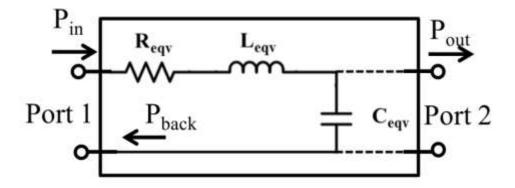

| Figure 2.4: Single conductor transmission line model of CNT interconnect.                                                                                                                                                                                                   | 33 |

| Figure 2.5: Length dependence resistance of SWCNT interconnect.                                                                                                                                                                                                             | 38 |

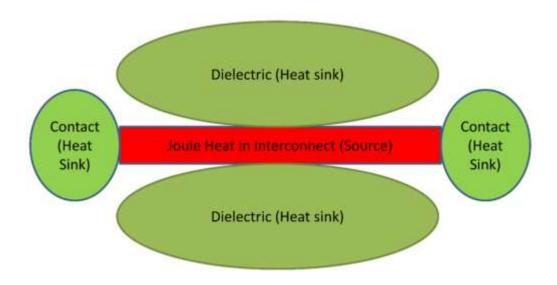

| Figure 2.6: Heat source and sinks in VLSI interconnect.                                                                                                                                                                                                                     | 43 |

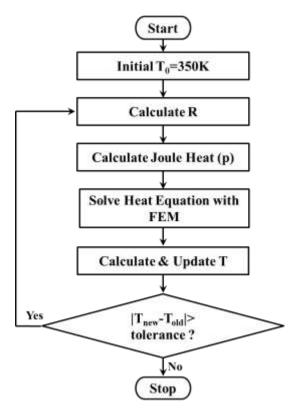

| Figure 2.7: Iterative solution to electrothermal coupled equations.                                                                                                                                                                                                         | 45 |

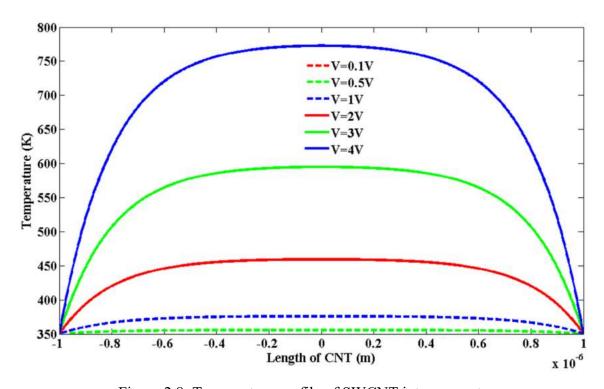

| Figure 2.8: Temperature profile of SWCNT interconnects.                                                                                                                                                                                                                     | 47 |

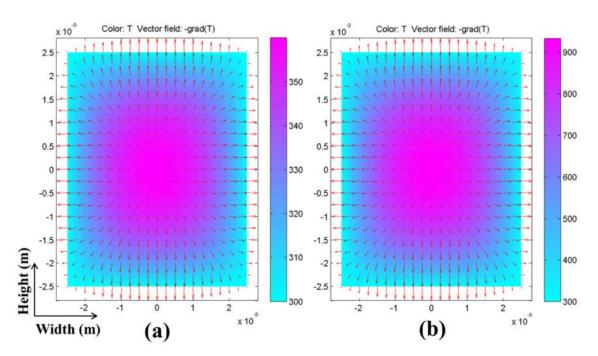

| Figure 2.9: Cross sectional temperature distributions (color) and heat flow vector (arrow) for 10 mA current bias (a) D =1nm, L=1 $\mu$ m, (b) D =4 nm, L=1 $\mu$ m. In case of (b) central shell temperature is above melting point (873K), therefore breakdown will occur | 48 |

| Figure 2.10: Temperature profile of MWCNT interconnect cross section.                                                                                                                                                                                                       | 49 |

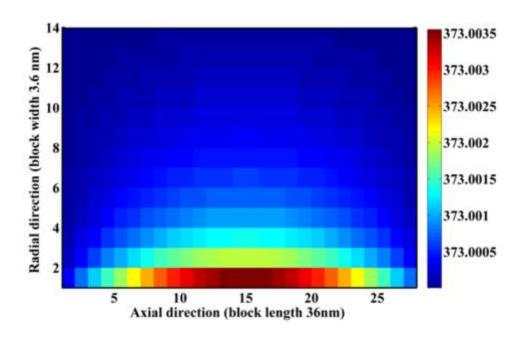

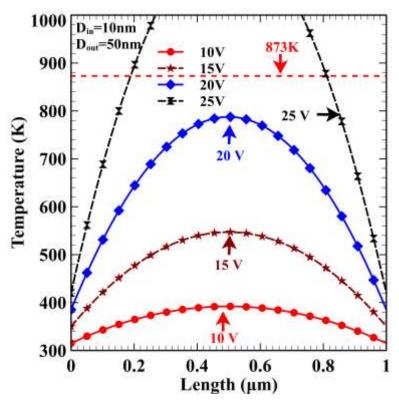

| Figure 2.11: Spatial variation of the temperature inside a MWCNT with Dout=50 nm and Din=10 nm. Note: Length is 1µm in these subfigures.                                                                                                                                    | 55 |

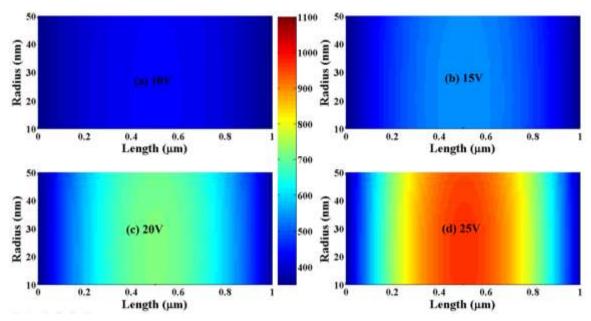

| Figure 2.12: Temperature distribution over the length of a MWCNT for different biasing voltages.                                                                                                                                                                            | 56 |

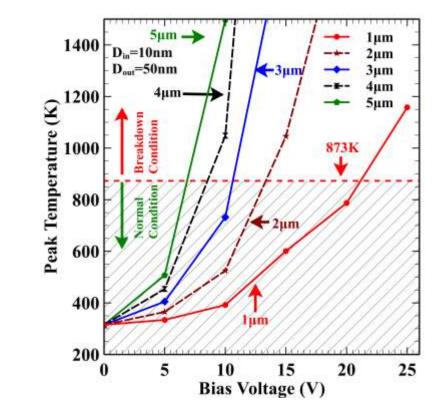

| Figure 2.13: Peak temperature at different biasing voltages for 1 to 5 µm long MWCNTs                                                                                                                                                                                       | 58 |

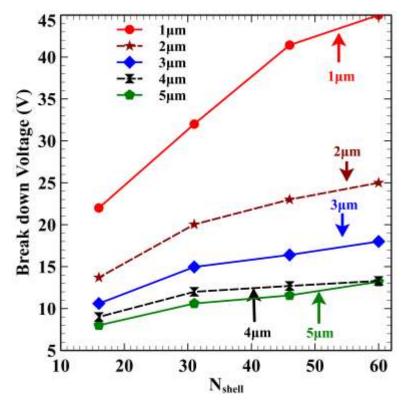

| Figure 2.14: Breakdown voltages for 1 to 5 µm long MWCNTs of different number of shells                                                                                                                                                                                     | 59 |

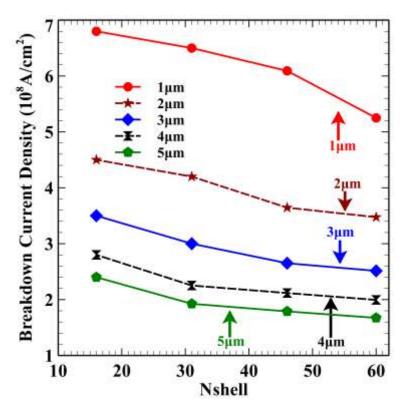

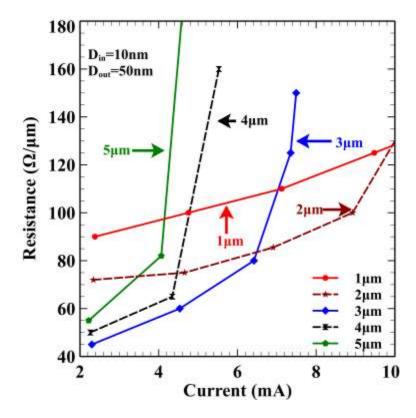

| Figure 2.15: Breakdown current for 1 to 5 µm long MWCNTs of different number of shells                                                                                                                                                                                      | 61 |

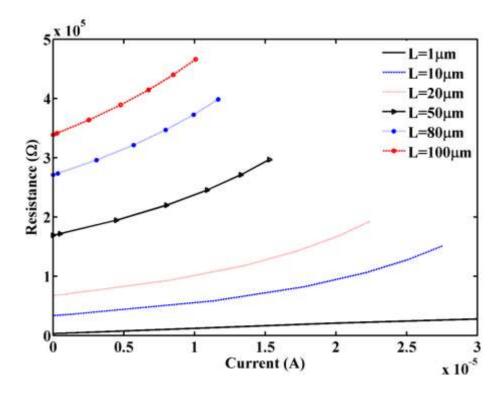

| Figure 2.16: Resistance of 1 to 5 µm long MWCNTs of different lengths                                                                                                                                                                                                       | 62 |

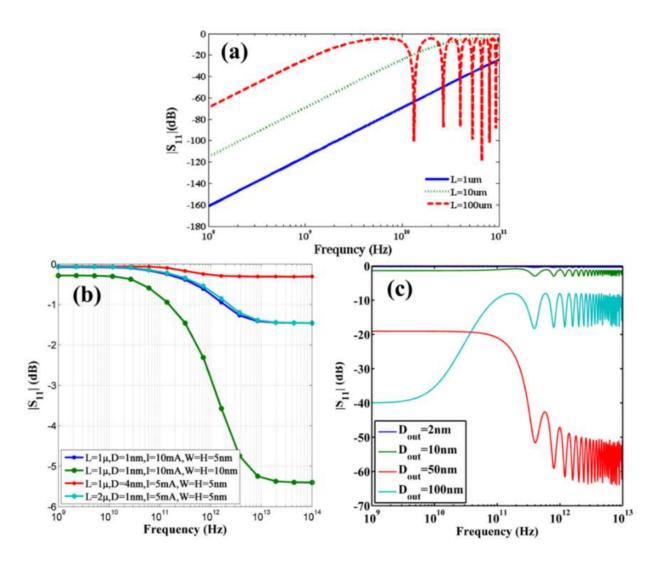

| Figure 2.17: Scattering parameter S11 of various interconnects (a) SWCNT, (b) SWCNT bundle based and (c) MWCNT (without interlayer dielectric)                                                                                                                              | 67 |

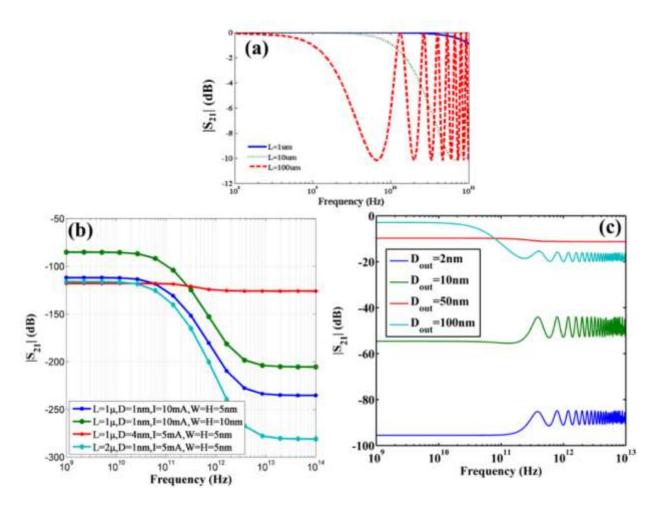

| Figure 2.18: Scattering parameter S21 of various interconnects (a) SWCNT, (b) SWCNT bundle based and (c) MWCNT (without interlayer dielectric)                                                                                                                              | 68 |

| Figure 2.18: Scattering parameter S21 of various interconnects (a) SWCNT, (b) SWCNT bundle based and (c) MWCNT (without interlayer dielectric)                                                                                                                                                                                                                                                                                                                                                    | 68  |

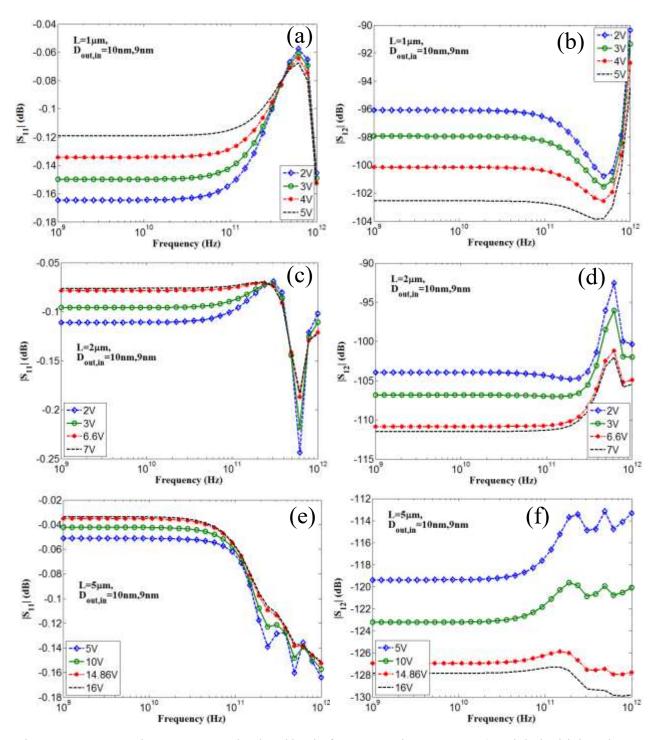

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.19: Scattering parameters $ S11 $ and $ S21 $ of MWCNT interconnect (modeled with interlayer dielectric effect) for different biasing voltages. MWCNT length in (a) and (b) is 1 $\mu$ m, in (c) and (d) 2 $\mu$ m. and in (e) and (f) 5 $\mu$ m. In each figure., Dout=10 nm, Din=9 nm.                                                                                                                                                                                                 | 69  |

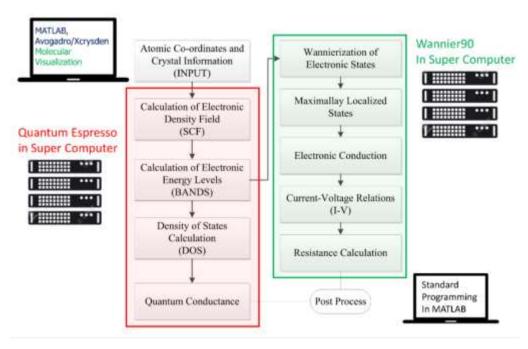

| Figure 3.1: Material simulation flow using various software and programming tools across various computational platforms                                                                                                                                                                                                                                                                                                                                                                          | 87  |

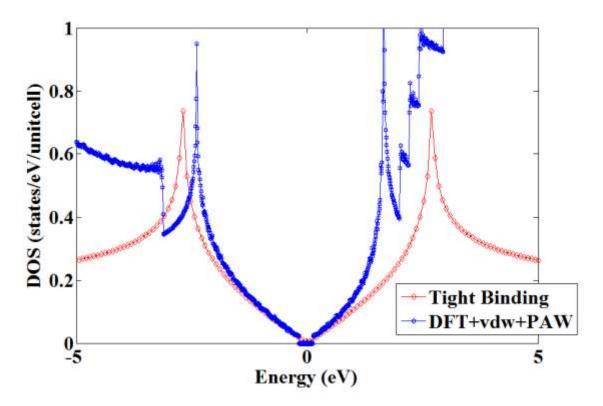

| Figure 3.2: Comparison of tight binding model and DFT. Here DFT accuracy has been increased by considering the Van der Waals correction (vdw) along with using plane augmented wave (PAW) implementation.                                                                                                                                                                                                                                                                                         | 88  |

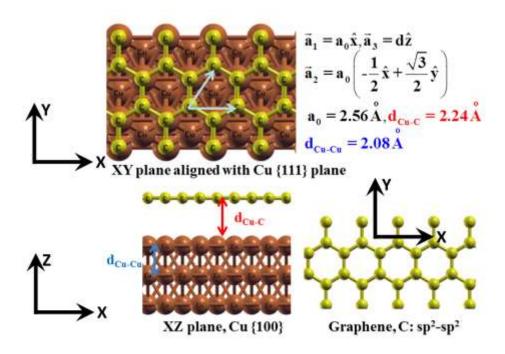

| Figure 4.1: Atomic structure of graphene on copper hybrid nano-interconnect in XY plane (top) and in XZ plane (bottom). Cu <111> plane is towards Cartesian Z-axis (which is XY plane). Lattice vectors for this system are shown on top right. Scale for the top, bottom and bottom-right are not same                                                                                                                                                                                           | 94  |

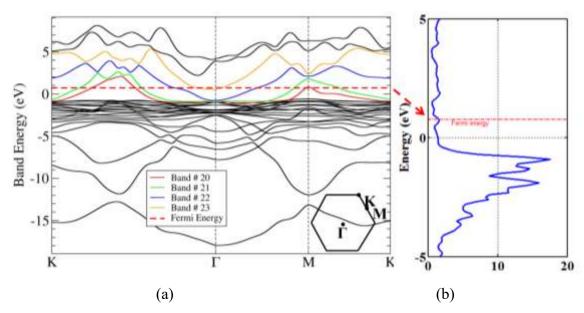

| Figure 4.2: (a) Band structure of G/Cu bulk system. Bands contributing to contstruct Fermi surface are high lighted with color. Fermi Energy is 0.7179 eV shown in red dashed line. At the bottom left corner of the band structure plot BZ special points are shown. (b) Density of States (DOS) from -5 eV to 5 eV are shown. Fermi energy is marked in DOS plot seperately with red dashed line. Unit of bulk DOS is states/eV/atom                                                            | 101 |

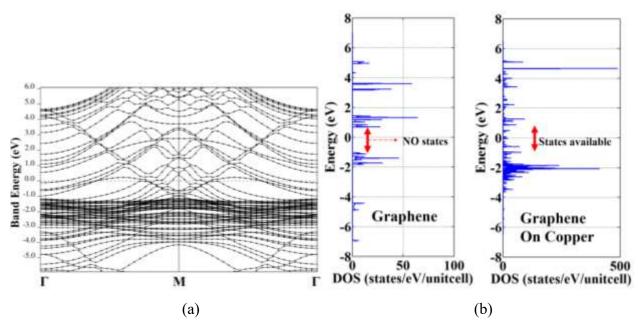

| Figure 4.3: (a) Electronic band structure of G/Cu nanoribbon. Fermi level at - 4.08 eV (b) Density of states of graphene interconnect are compared with graphene/copper interconnect. Fermi energy is set to 0 eV in (a) and (b) for the purpose of comparison of two different material systems. Near the Fermi energy, there are no states available for the graphene interconnect.                                                                                                             | 102 |

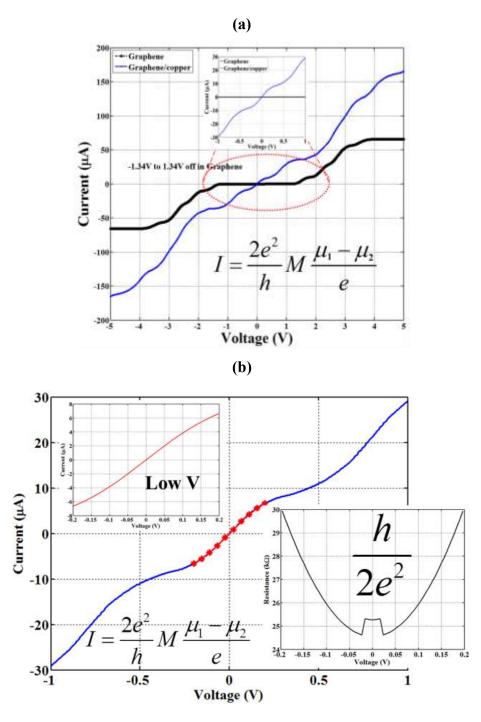

| Figure 4.4: (a) Current voltage (I-V) characteristics of G/Cu nanoribbon interconnect compared with graphene only interconnect. For graphene, no current is observed between -1.34 V to 1.34 V because of not having available states in that energy window. However, for graphene on copper is still conductive in this window. (b) I-V characteristics of G/Cu with lower bias voltage. Top inset shows linear region near zero bias and lower inset shows resistance versus voltage relations. | 103 |

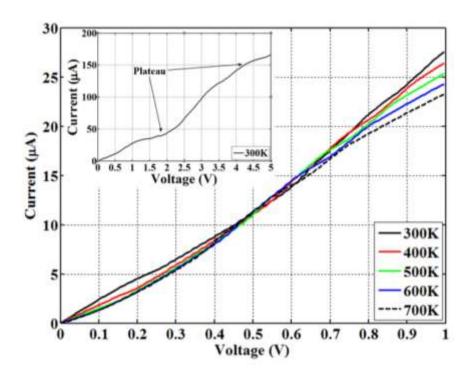

| Figure 4.5: I-V characteristics of G/Cu interconnect at different temperatures. Inset shows I-V characteristics for 0 to 5V bias with several plateaus                                                                                                                                                                                                                                                                                                                                            | 105 |

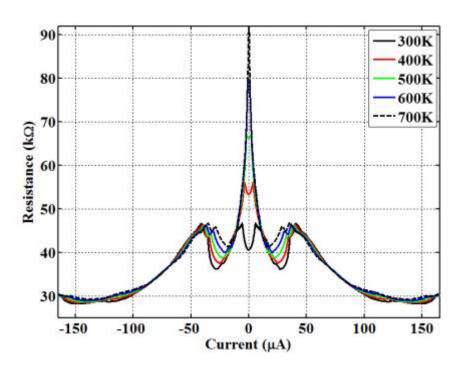

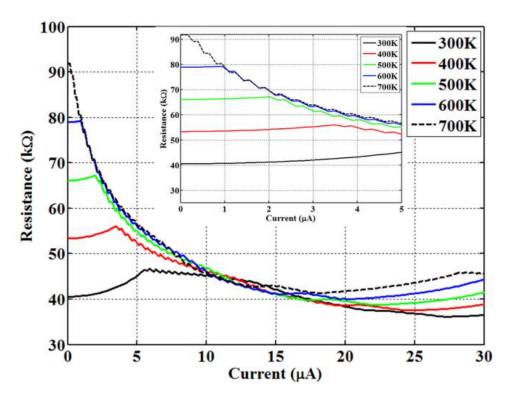

| Figure 4.6: Resistance versus current at different temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                   | 106 |

| Figure 4.7: Resistance versus current at low bias current                                                                                                                                                                                                                                                                                                                                                                                                                                         | 107 |

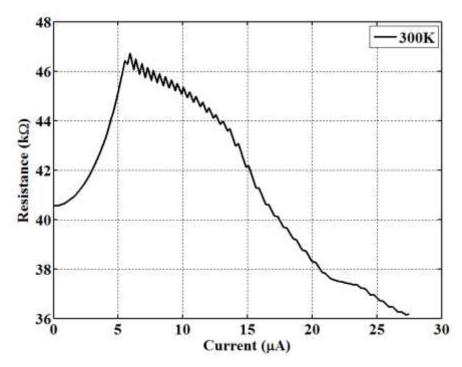

| Figure 4.8: Resistance versus current variation at room temperature. Resistance decreases with increase in biasing current due to plateau in I-V characteristics                                                                                                                                                                                                                                                                                                                                  | 108 |

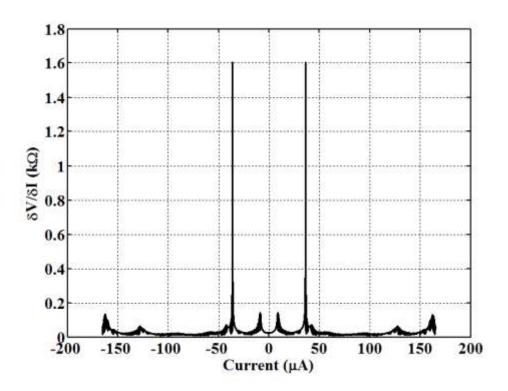

| Figure 4.9: Differential resistance versus current.                                                                                                                                                                                                                                                                                                                                                                                                                                               | 111 |

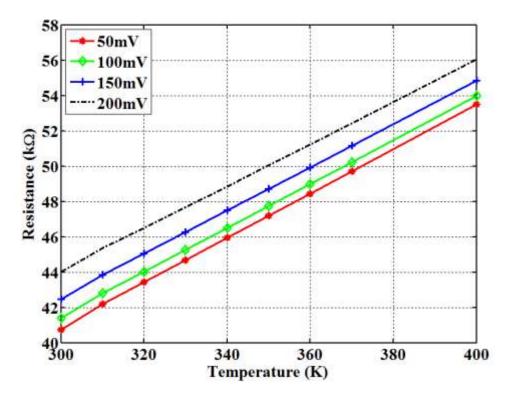

| Figure 4.10: Temperature dependent resistance at different bias voltages                                                                                                                                                                                                                                                                                                                                                                                                                          | 112 |

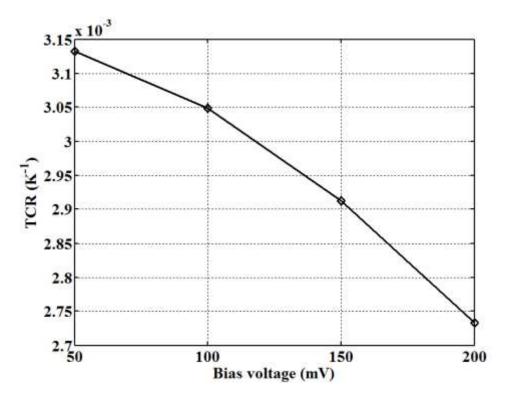

| Figure 4.11: Temperature coefficient of resistance change with bias voltage                                                                                                                                                                                                                                                                                                                                                                                                                       | 113 |

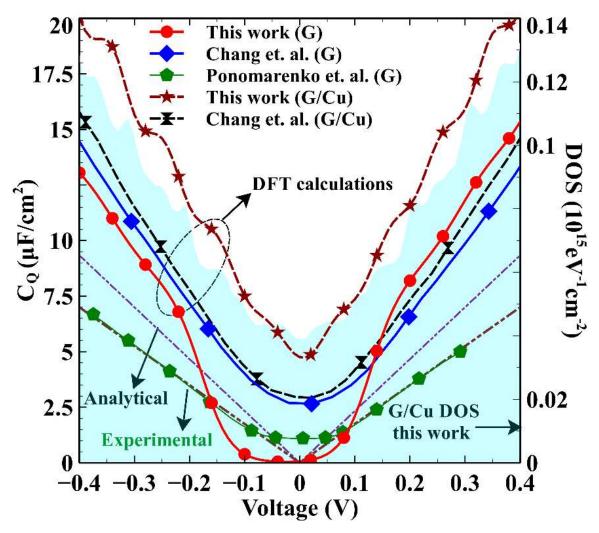

| Figure 5.1: Comparison of quantum capacitances (CQ) of graphene (G) and graphene on copper (G/Cu) in 2D systems in between this work and earlier works. Shaded area is DOS of G/Cu in 2D (scale is in the right side of this plot) | 121 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

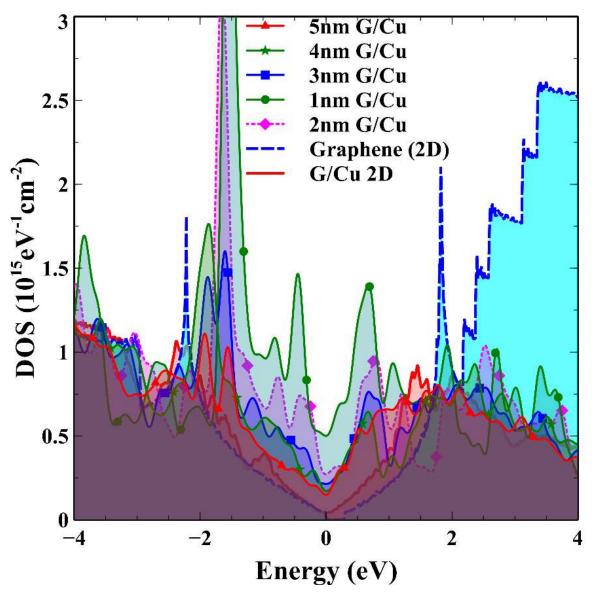

| Figure 5.2: Density of states of graphene (G) and graphene/copper nanoribbon (G/Cu-NR) for various width are shown for comparison. Scales for all these subfigures are different                                                   | 122 |

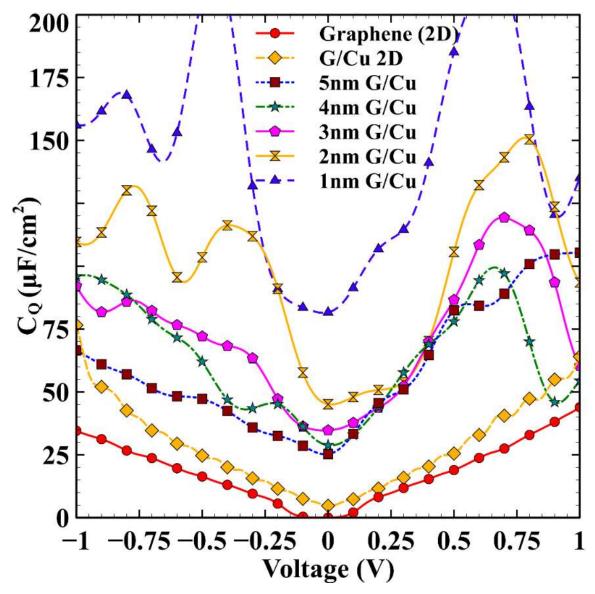

| Figure 5.3: Calculated quantum capacitances at different potentials of graphene                                                                                                                                                    | 123 |

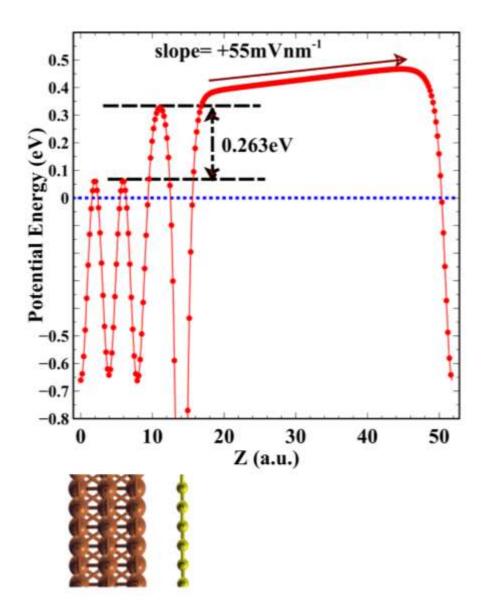

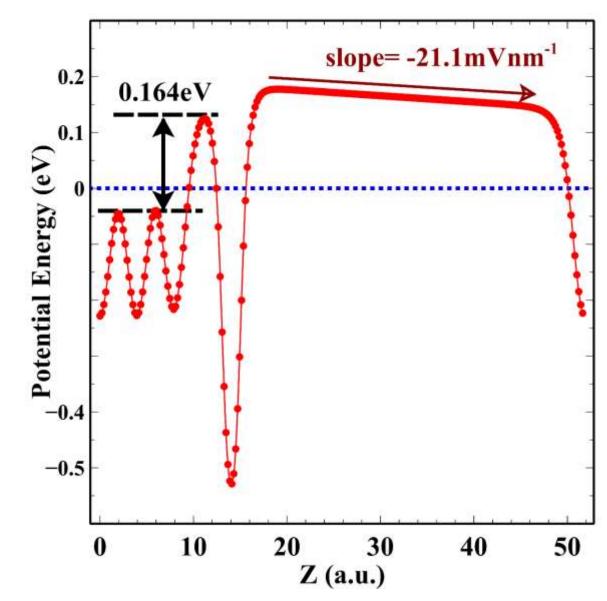

| Figure 5.4: Macroscopically averaged plane potential at graphene-copper junction of 2D. Note: 1 atomic unit (a.u) =0.529 Å.                                                                                                        | 125 |

| Figure 5.5: Macroscopically averaged plane potential at graphene-copper junction of 1nm width G/Cu-NR. Note: 1 atomic unit (a.u) =0.529 Å                                                                                          | 126 |

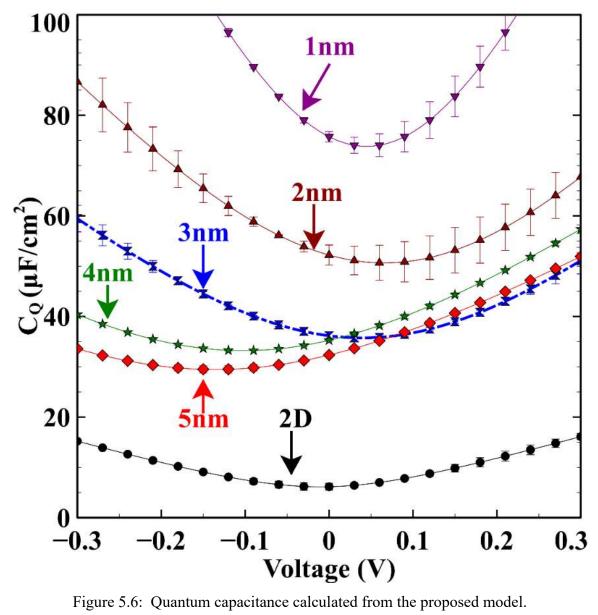

| Figure 5.6: Quantum capacitance calculated from the proposed model.                                                                                                                                                                | 131 |

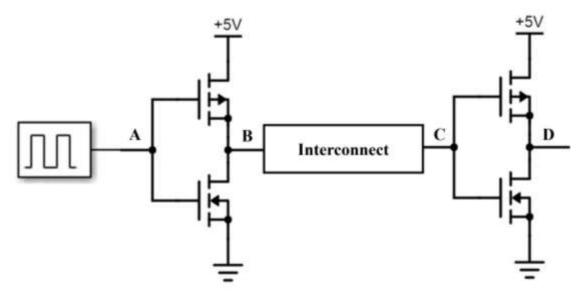

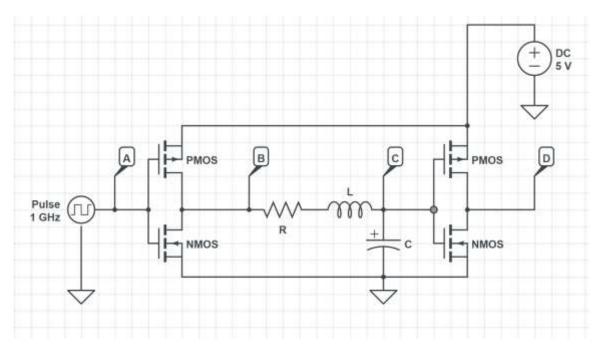

| Figure 6.1: Inverter pair with an emerging interconnect in between.                                                                                                                                                                | 134 |

| Figure 6.2: SPICE Implementation of CMOS inverter pair with interconnect in between                                                                                                                                                | 139 |

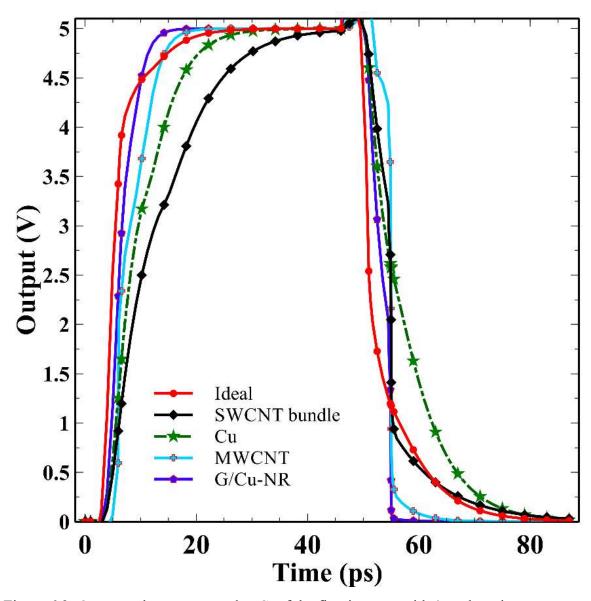

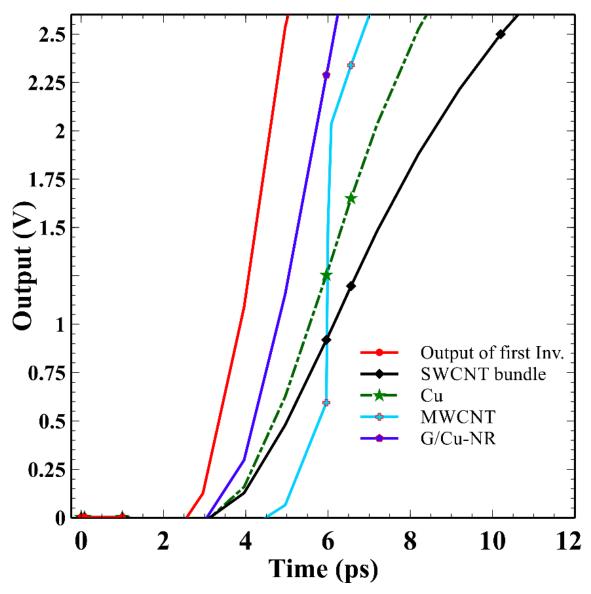

| Figure 6.3: Output voltage measured at C, of the first inverter with 1μm long interconnect of various materials.                                                                                                                   | 140 |

| Figure 6.4: Estimation of delay at 2.5V level of signal.                                                                                                                                                                           | 141 |

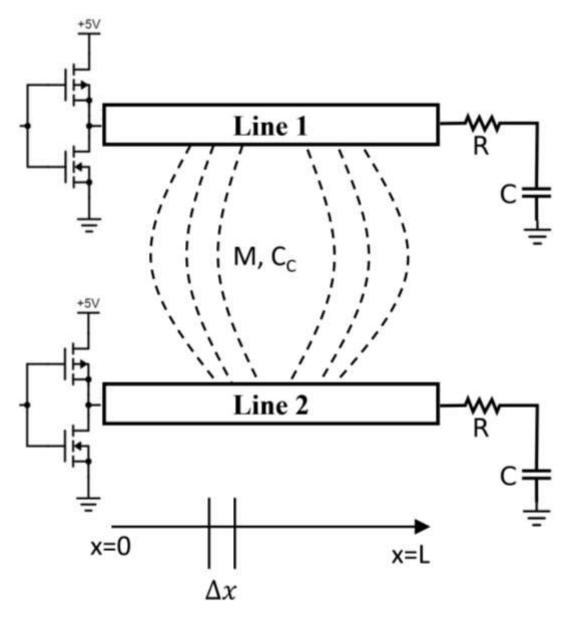

| Figure 6.5: Coupled interconnect lines with mutual inductance (M) and coupling capacitance                                                                                                                                         | 144 |

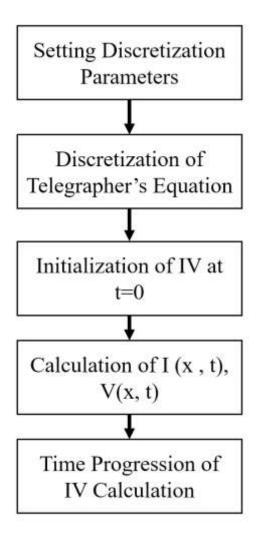

| Figure 6.6: Implementation step for FDTD technique.                                                                                                                                                                                | 147 |

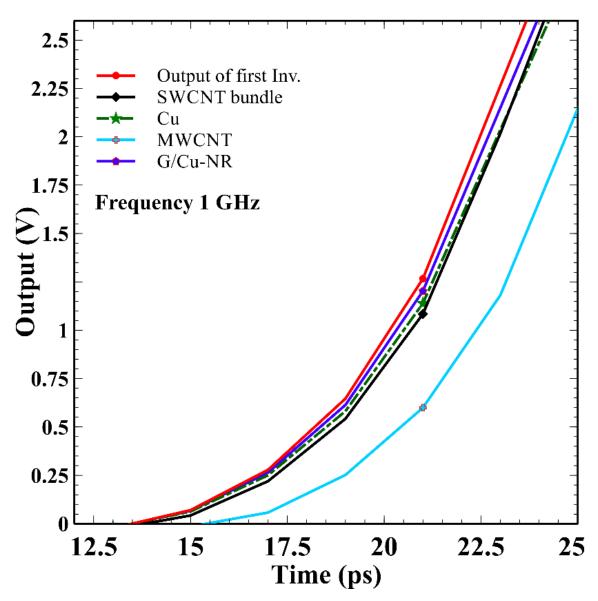

| Figure 6.7: FDTD delay of a 1 µm long interconnect with a 5 nm by 5 nm cross section in between pair of inverters at 1 GHz frequency                                                                                               | 148 |

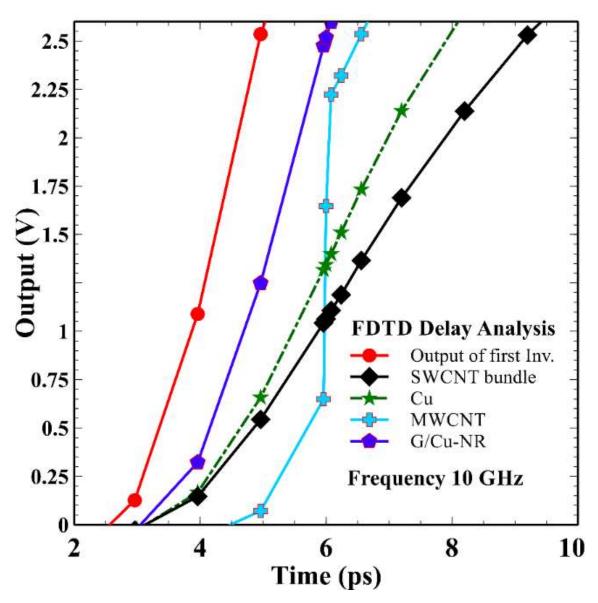

| Figure 6.8: FDTD delay of a 1 µm long interconnect with a 5 nm by 5 nm cross section in between pair of inverters at 10 GHz frequency                                                                                              | 149 |

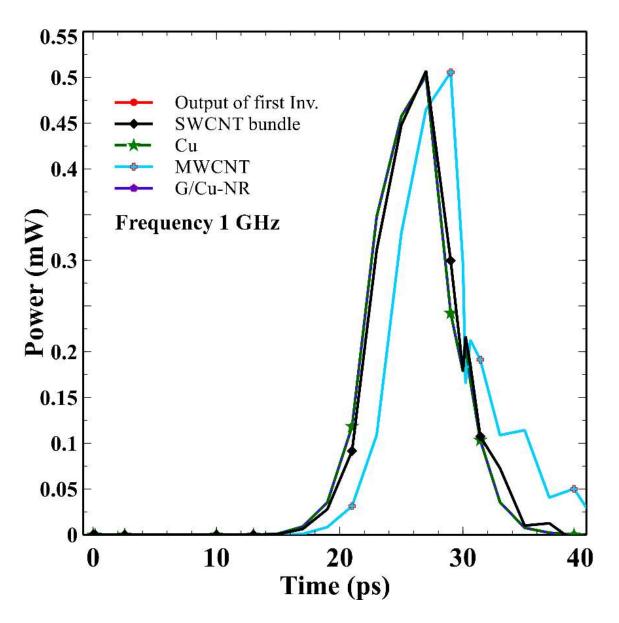

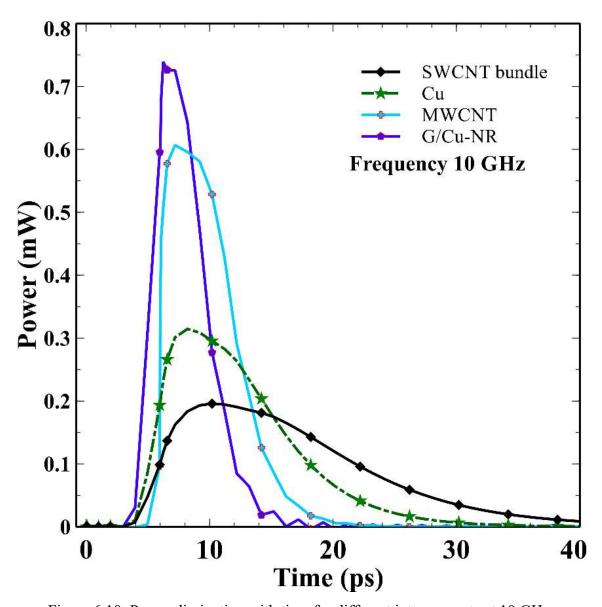

| Figure 6.9: Power dissipation with time for different interconnects at 1 GHz.                                                                                                                                                      | 152 |

| Figure 6.10: Power dissipation with time for different interconnects at 10 GHz.                                                                                                                                                    | 153 |

#### **ABSTRACT**

This work studies various emerging reduced dimensional materials for very large-scale integration (VLSI) interconnects. The prime motivation of this work is to find an alternative to the existing Cu-based interconnect for post-CMOS technology nodes with an emphasis on thermal stability. Starting from the material modeling, this work includes material characterization, exploration of electronic properties, vibrational properties and to analyze performance as a VLSI interconnect. Using state of the art density functional theories (DFT) one-dimensional and two-dimensional materials were designed for exploring their electronic structures, transport properties and their circuit behaviors. Primarily carbon nanotube (CNT), graphene and graphene/copper based interconnects were studied in this work.

Being reduced dimensional materials, the charge carriers in CNT(1-D) and in graphene (2-D) are quantum mechanically confined. As a result of this, free electron approximation fails to explain their electronic properties. For same reason, Drude theory of metals fails to explain electronic transport phenomena. In this work Landauer transport theories using non-equilibrium Green function (NEGF) formalism was used for carrier transport calculation. For phonon transport studies, phenomenological Fourier's heat diffusion equation was used for longer interconnects. Semi-classical BTE and Landauer transport for phonons were used in cases of ballistic phonon transport regime. After obtaining self-consistent electronic and thermal transport coefficients, an equivalent circuit model is proposed to analyze interconnects' electrical performances.

For material studies, CNTs of different variants were analyzed and compared with existing copper based interconnects and were found to be auspicious contenders with integrational challenges. Although, Cu based interconnect is still outperforming other emerging materials in terms of the energy-delay product (1.72 fJ-ps), considering the electromigration resistance graphene Cu hybrid interconnect proposed in this dissertation performs better. Ten times more

electromigration resistance is achievable with the cost of only 30% increase in energy-delay product. This unique property of this proposed interconnect also outperforms other studied alternative materials such as multiwalled CNT, single walled CNT and their bundles.

#### CHAPTER 1 INTRODUCTION

The metal oxide semiconductor field effect transistor (MOSFET) has been the workhorse for semiconductor industries for more than half a century. Interconnect is the highway for electrical signal to travel through the (computer) chip and is commonly known as integrated circuit (IC). Interconnect is referred as a pathway for electrical charge carriers (electrons) to travel through based on the potential differences of the source and destination nodes. In most cases materials with metallic behavior or highly doped silicon (degenerate, poly-Si) could be used as interconnect. Any materials that show no band gap in its electronic band structure is metallic in nature and can be potentially used as interconnect. Besides zero band gap, it is preferred having high density of states near Fermi energy to be a very good conducting interconnect material.

If a transistor is the information processing unit, one can think of interconnect as a connector of all those information processing units. Beside speedy transistor, it also requires to have high speed interconnect in order to obtain superior overall system performance. Besides, providing pathways for electrical signals, interconnects also facilitate the supply of electrical powers to all processing nodes for their function. Any fault and failure in any interconnect line may compromise fidelity of information or lead to the failure of the entire chip. In current technology, more than 50% of capacitance in a CMOS IC is due to interconnects. As a result, more than 50% of dynamic power is consumed by interconnects [1]. This is why interconnect technologies require critical attention alone, with the transistors in a chip.

<sup>\*</sup>Part of the work is reported in the following publication:

A. Srivastava and K. M. Mohsin, "Thermal effects in carbon nanotube VLSI interconnects," *Nano-CMOS and Post-CMOS Electronics: Circuits and Design*, Institution of Engineering and Technology Press, 2016, pp. 172-200.

The more processing units an IC has, the more computation it can perform and as a result more connectors will be necessary. This has been the basic principle of 'scaling' for interconnects where by reducing the physical size of the interconnect, further interconnect paths can be placed to fit into a given chip area. At the same time since electrons will have to travel a shorter distance signal propagation speed will be increased. The idea goes back to 1965, when founder of Intel's Gordon Moore forecasted the increase functionality of ICs, commonly known as 'Moore's Law'. The law states that the number of transistors in an IC would double every 18 months. For nearly five decades, semiconductor industries have fulfilled the prediction of this rule by constantly pushing the computer chip technology and maintained a tremendous effort spanning from material selection, fabrication process and novel architectures to keep the progress uncompromised. However, Moore's law may be reaching its end and a new paradigm shift with a lot more interesting things are on the way [2].

#### 1.1. Present Technology and Its Limitations

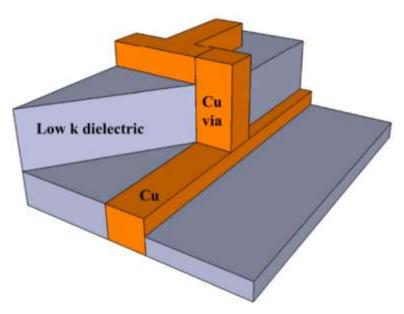

In present CMOS technology, copper is used as an interconnect material buried in low-k dielectric as shown in Fig.1.1[3] which started at the 220 nm technology node in 1997 introduced by IBM. For several reasons Cu successfully replaced Al (aluminum), a standard technology for chip makers for a long period. The key benefits of using Cu instead of Al are listed briefly in the following,

- 1. Cu offers 40% less resistivity than Al

- 2. RC delay decreases by 15%

Figure 1.1: Cu/low-k interconnect technology.

- 3. More durable than Al with 100 times more reliability

- 4. Scalability of Cu is better than Al

- 5. Cu enables multiple layers of interconnect deposition with damascene technique

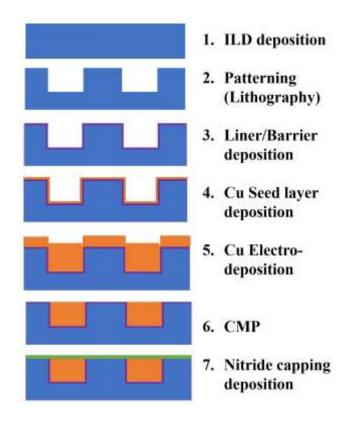

To reduce interference between two adjacent signals interconnect lines, low-k dielectric ( $\epsilon_r < 3$ ) is being used as an interlayer dielectric (ILD) in present CMOS interconnect technology. For patterning Cu lines in a semiconductor chip, damascene technique [4] along with electrodeposition [5] is being used widely. However, unlike Al, Cu is more diffusive in to the interlayer dielectric. This is why a barrier layer is required to keep the metal-dielectric interaction minimum. First step of interconnect technology starts with the photolithography which is a essential step for patterning of metal lines on the previously deposited dielectric layer. Then on the patterned substrate, a barrier layer of tantalum on tantalum nitride (Ta/TaN) or titanium on titanium nitride (Ti/TiN) is deposited. The purpose of the first metal layer (Ti or Ta) is to increase the adhesion between the metal and dielectric layers. The purpose of the second layer, which is essentially a nitride (either TaN or TiN), is to stop Cu diffusion into dielectric. After deposition of this Ti/TaN (or Ta/TaN), a Cu seed layer is deposited by chemical vapor deposition (CVD). This seed layer works as a liner for the electro-chemical deposition of Cu.

Electro-chemical deposition is the main Cu layer deposition step in present interconnect technology. A process called chemical and mechanical polishing (CMP) is being used to planarize the deposited Cu layer. This completes one cycle of damascene technique for Cu deposition. To protect the deposited Cu lines from the top surface a capping layer usually silicon nitride is being used widely. After this silicon nitride, another layer of interlayer dielectric is being deposited which is followed by the next damascene process. This process repeats for several times for each

layer of metallization. Currently, 4-7 metal layers are being used by industry widely. In Fig. 1.2, a summary of current interconnect process technology is presented.

A rapid down scaling of MOSFETs happened following the Moore's law. In lieu of the continuous downsizing of transistors, interconnect technology also requires to be scaled down to get maximum benefit of downsizing. However, scaling down of Cu/low-k interconnect is suffering increased heating, electro-migration and void formation [6, 7].

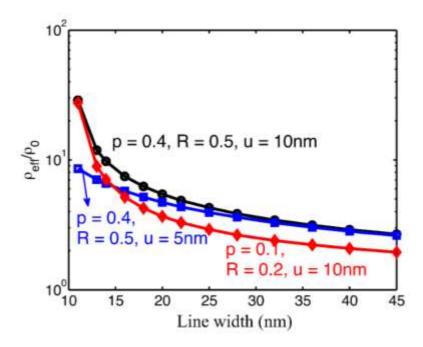

In scaling of interconnects, low-dimensional effects dominate over the bulk properties of materials. Fig. 1.3 shows how resistivity of Cu line is deviating from its bulk resistivity value when line width approaches 10 nm [8]. In Fig. 1.3, p, R and u stands for specularity parameter, surface reflectivity and grain size respectively. Due to decreased volume, Joule heat generation per unit volume increases which causes resistance to increase. Metal ions in interconnect materials are swept by the high electric field and causes void formation which is known as electromigration. On top of this electro-migration, Joule heating makes things worse. Due to Joule heating, center of interconnect reaches the melting point of the material and thermal run away causes open circuit. While void and open circuit formation due to electro-migration may happen after long periods of use, Joule heating may happen right after few clock cycles of use. These reliability issues are serious bottlenecks in scaled CMOS technology nodes.

Figure 1.2: Current interconnect (Cu/low-k) process technology.

Figure 1.3: Increasing line resistance of Cu-low/k interconnect in scaled technology nodes.

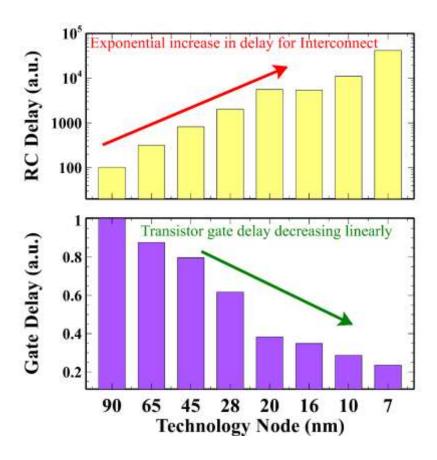

As it has been presented in Fig. 1.4, interconnect delay is exponentially increasing with the shrinking down of technology nodes while transistor gate delay is decreasing linearly. Therefore, interconnect RC delay is dominant over the transistor gate delay [9].

Electromigration (EM) is a mechanism where gradual migration of metallic ions occurs due to electron drag. EM poses another reliability threat for present CMOS interconnect technology. When Joule heating is present on top of EM, interconnect life time decreases significantly. Fig. 1.5 illustrates EM effect and the related breakdown. Because of EM, void formation worsens over time and creates a complete open circuit. This open circuit may cause the failure of the entire or any vital part of the chip. This void formation is more frequent near the corner of the metal line bending.

#### 1.2. Alternative Approaches

Due to the above-mentioned reasons, researchers are continuously in search of better interconnect technology. Following is a summary addressing all these problems in order to find new interconnect technology.

**Emerging materials:** Emerging materials might possibly give a better electro-thermal conductivity in solving present interconnect technology. New novel materials could be used for charge transport channel, low-k dielectric, interconnect capping, adhesive and liner/barrier. Efforts are being made to find a novel material to replace existing Cu-low-k dielectric.

Alternative state variable: Instead of charge carrier transport, some other state variable could be useful in scaling down interconnect technology. Following are few examples of alternate state variable.

Figure 1.4: Comparison of transistor gate delay with interconnect's RC delay.

Figure 1.5: (A) Electromigration phenomena (B) Nanogap formation due to electromigration.

Electron's spin: As spintronic is evolving, researchers are also deploying spin transport techniques instead of charge transport in Si [12], metals [13], and graphene [14, 15]. Work is progressed in spin injection [16], transport and detection to realize spin interconnects [12-18]. Spin manipulation works in a very small energy scale and that is why spin interconnect will dissipate less heat than charge transport based interconnect.

**Photon:** Instead of electron, an optical interconnect works as a wave guide for photons. Since, photon is quanta of light and travels at the speed of light there will be lightning speed in signal transmission across the chips. In very high frequency applications (THz regime) metallic interconnect will fail to transport electrical signal due to increased dielectric loss and increased dynamic power. Hence, optical interconnect will be necessary in high frequency applications and also to obtain unprecedented floating point operations (FLOPS) and corresponding read/write operation [19]. Substantial research has been done in realizing photonics circuits and systems [20].

**Phonon:** Phonon works as the state variable and a rapidly growing research area called "Phononics" deals with phonon generation, injection and transport [21]. This state variable which is basically quantized atomic vibration modes of atoms was exploited in THz applications as a future interconnect [22].

Beyond above mentioned state variable "plasmon" and "excitons" are also very vibrant filed of research as an alternate state variable to "charge". These are few of many frontiers to address the interconnect issues. In this dissertation, emerging materials based solutions were looked for present interconnect technology.

#### 1.3. Organization

In Chapter 2, carbon nanotubes application as a VLSI interconnect is discussed and a model is proposed to incorporate Joule heating effect into electrical performances. In Chapter 3, a theoretical ground of materials modeling for rest of the dissertation is presented. Density functional theory (DFT) techniques is the center point of this chapter. In Chapter 4, electrical properties of graphene on copper nanoribbon (G/Cu-NR) based interconnects are discussed. Electrical resistivity is estimated from the DFT calculations. In Chapter 5, quantum capacitance of G/Cu-NR which is a very crucial parameter for low dimensional system is reported. In Chapter 6, and application demonstration has been shown for the proposed interconnect materials. Future work is elaborated followed by conclusion in chapter 7. In appendices, necessary codes, simulation parameters and material data are provided.

# CHAPTER 2 ELECRTRO-THERMAL TRANSPORT OF CNT BASED VLSI INTERCONNECT

#### 2.1. Introduction

After the discovery of carbon nanotube (CNT) in 1991 by Iijima [23] many researchers envisioned it as the next generation interconnect material [24]. Numerous theoretical and experimental researches reached to the conclusion that CNT is the right choice of material due to its excellent electro-thermal properties [25-28]. In Table 2.1, few properties relevant to CNT VLSI interconnect technology are summarized and compared it to that of Cu. As shown in Table 2.1, different variants of CNT have two orders of more current capacity than Cu, and 5 to 10 times more thermal conductivity. Due to these exotic properties, researchers not only explored this carbon based material as the VLSI interconnect [24-27, 29, 30] but also as sensors [31, 32] and devices [33-36]. In interconnect design, one not only depends on superior electronic properties but also looks into thermal properties to avoid Joule heating induced thermal breakdown.

<sup>\*</sup>Part of the work is reported in the following publication:

<sup>1.</sup> K. M. Mohsin, A. Srivastava, "Modeling of Joule heating induced effects in multiwall carbon nanotube interconnects," IEEE Transaction VLSI, vol. 25, no. 11, pp. 3089-3098, Nov., 2017.

<sup>2.</sup> K. M. Mohsin, A. Srivastava, A. K. Sharma, and C. Mayberry, "A thermal model for carbon nanotube interconnects," Nanomaterials, vol. 3, no. 2, pp. 229-241, April 26, 2013.

<sup>3.</sup> K. M. Mohsin, and A. Srivastava, "Characterization of SWCNT bundle based VLSI interconnect with self-heating induced scatterings," Proc. GLSVLSI '15, pp. 265-270, 2015.

<sup>4.</sup> K. M. Mohsin, Y. M. Banadaki, and A. Srivastava, "Metallic single-walled carbon nanotube based temperature sensor with self-heating," Proc. SPIE (Smart Structures/NDE: Nano-Bio-, and Info-Tech Sensors and Systems: SSNO6), pp. 906003-906003-7, 2014.

<sup>5.</sup> K. M. Mohsin, A. Srivastava, A. K. Sharma, and C. Mayberry, "Characterization of MWCNT VLSI interconnect with self-heating induced scatterings," Proc. IEEE Computer Society Annual Symposium on VLSI, pp. 368-373, 2014.

<sup>6.</sup> A. Srivastava, and K. M. Mohsin, "Thermal effects in carbon nanotube VLSI interconnects," *Nano-CMOS and Post-CMOS Electronics: Circuits and Design*, Institution of Engineering and Technology Press, 2016, pp. 172-200.

Table 2.1: Thermoelectric properties of Cu, SWCNT and MWCNT

| Properties                                               | Cu       | SWCNT          | MWCNT                      |

|----------------------------------------------------------|----------|----------------|----------------------------|

| Max current density (A/cm <sup>2</sup> )                 | $10^{7}$ | >109           | >109                       |

| Melting point (K)                                        | 1356     | 870 [37]       | 3000-4000*                 |

| Thermal conductivity (Wm <sup>-1</sup> K <sup>-1</sup> ) | 385      | 1750-6000 [38] | 3000 [39]                  |

| Mean free path (µm)                                      | 0.04     | ~1             | 25 (100 nm outer diameter) |

<sup>\*</sup>Reported in literatures to be close to the melting point of graphite.

Since CNT has high thermal conductivity it can quickly drain out the generated heat into the dielectric. This is why it is perceived that different variants of CNT interconnects will be inherently more thermally stable than the Cu based interconnect [25, 40]. In explaining electrical properties, Srivastava et al. [27, 41] explained how to use one dimensional fluid based model for SWCNT and MWCNT interconnects. Single conductor based transmission line model has been proposed by Sarto and SPICE compatible circuit models have been proposed by D' Amore et al. [42, 43]. Most of these works highlighted the electronic properties and overlooked the thermal stability. Chiang et al. [44] addressed the issue of Joule heating induced performance degrading of Cu-low-*k* interconnects. However, not much is reported in literature on Joule heating induced scattering, which is a serious roadblock in achieving the large current density. Pop [37] studied thermal break-down in metallic SWCNT with Fourier heat equation. One-dimensional Fourier heat equation has been used by Yamada et. al. [45] and Kitsuki et. al. [46] to explain experiments of carbon nanofiber thermal breakdown. Further literatures will be provided when necessary in the rest of the chapter in discussing all three variants of CNT.

#### 2.2. Electrical Properties of CNTs

A CNT is rolled up in a single layer graphene sheet consisting sp<sup>2</sup> hybridized carbon atoms with 0.142 nm bond length as shown in Fig. 2.1. Depending on the number of layers of graphene, CNT could be single walled (SWCNT) or have multiple walls (MWCNT). Geometry of a SWCNT is just a hollow cylinder while MWCNT consists of multiple concentric cylindrical shells. Each of these shells is a rolled over single layer sp<sup>2</sup>- sp<sup>2</sup> hybridized sheet of carbon atoms. Hence, MWCNT is a piling of concentric multiple SWCNTs where each shell has essentially different diameters. All the layers are bonded by the weak Van der Waals attraction forces with bonding length 0.34 nm [47]. Beside naturally obtained bundle of SWCNT and MWCNT or any of their mixed kind, it is also possible to use isolated SWCNT or MWCNT as VLSI interconnect. In this chapter, focus is only on SWCNT, MWCNT and SWCNT bundle. Same approaches can be applied for MWCNT bundle and any kind of mixed bundle. In the next section, electrical properties of different CNTs will be discussed.

Figure 2.1: Different carbon-based nanomaterials.

#### **2.2.1.** Equivalent Resistance $(R_{eqv})$

An isolated SWCNT can be implemented in between metal contacts as interconnecting wire as shown in Fig. 2.2. Earlier it was challenging to align SWCNTs in between the contacts but recently that has been implemented successfully [48]. For interconnect applications, SWCNT can also be replaced by MWCNT or SWCNT bundle to get a better performance in terms of current capability. Electrically SWCNT can be approximated as one-dimensional conductor [49]. MWCNT or SWCNT bundle can be approximated as parallel SWCNTs. In case of MWCNT, all the shells are concentric and shell diameters are necessarily different. However, in SWCNT bundle it is not necessary to have different shell diameters.

SWCNT bundle shown in Fig. 2.1 is of same shell diameter. In this section, a set of general formulae to estimate electrical properties applicable to these three variants of CNT are presented. From Landauer-Büttiker, formalism, dc resistance of a CNT shell,  $R_k$ , can be calculated from Eq. (2.1).

$$R_{k} = \frac{h}{2q^{2}} \frac{1}{M_{k}} \left( 1 + \frac{L}{\lambda_{eff}(L, D_{k}, T_{k}, V)} \right)$$

(2.1)

where different parameters are defined as follows:

L =length of interconnect,

$D_k$  = diameter of  $k^{th}$  shell in MWCNT or in SWCNT bundle,

$T_k$  = temperature of k<sup>th</sup> shell,

q = electronic charge,

h = Plank constant,

Figure 2.2: SWCNT based VLSI interconnects.

$\lambda_{eff}$  = effective mean free path of an electron,

$M_k$  = equivalent conducting channels (spin degenerate), and

*V*= biasing voltage across interconnect.

The effective mean free path,  $\lambda_{eff}$  takes into account the electron scattering with acoustic and optical phonons and will be discussed in Section 2.4.4. For SWCNT,  $D_k$  is just the shell diameter of CNT.

The first term in Eq. (2.1) is quantum in nature and the second term is a diffusive resistance, which is proportional to the length. It is apparent from Eq. (2.1) that even for the zero length, resistance is nonzero because of the first term, quantum resistance. This nonzero resistance is due to the effect of contacting quantum channels. Each spin channel contributes to  $h/q^2$  resistance. Considering spin "up" and "down" running parallel, overall resistance for each channel is  $h/2q^2$ . Now considering  $M_k$  as the average number of transport channels in each shell the total quantum resistance will be the first term in Eq. (2.1). The "contact resistance" should not to be confused with this first term, quantum resistance. It is the contribution of contact in intrinsic part of the interconnect. To clarify further, here only CNT resistance is taken in to account not considering "CNT-metal" interface resistance or "contact resistance". Hence, to get the total resistance including contacts one requires adding contact resistance. Otherwise, this Eq. (2.1) will only compute the intrinsic resistance of the materials at hand. The inclusion of "CNT-metal" contact resistance into the model can be obtained by Eq. (2.4). The discussion of this contact resistance followed by Eq. (2.4).

For SWCNT there is only one shell. However, for MWCNT and SWCNT bundle different shells could be at different temperatures. This is why in Eq. (2.1),  $T_k$  has been introduced to take

into account the temperatures of different shells.  $M_k$  is the equivalent conducting spin degenerate channels of interconnect. For metallic SWCNT it is 2. Statistically for naturally obtained SWCNTs, 1/3 are metallic and 2/3 semiconducting. From statistics, one can estimate  $M_k$  value of any kind of CNT interconnect with the following equation [50],

$$M_{k} = \begin{cases} \frac{2}{3} & for D_{k} < \frac{1900}{T_{k}} \\ a_{1}D_{k}T_{k} + a_{2} & for D_{k} > \frac{1900}{T_{k}} \end{cases}$$

(2.2)

Where,  $a_1$  and  $a_2$  are fitting parameters. It is noteworthy that spin degeneracy has been taken into account in Eq. (2.2). Fitting parameters  $a_1$  and  $a_2$  take the values as  $3.26 \times 10^{-4}$  nm<sup>-1</sup>K<sup>-1</sup> and -0.08, respectively. Since Eq. (2.2) has been calculated from the knowledge of band structure, it can be used reliably as a compact equation for quick estimation of resistance of interconnect without any detail calculations. Now from Eqs. (2.1) and (2.2), the resistance of each CNT shell can be obtained regardless of whether they are metallic or semiconducting. Equivalent resistance of MWCNT or SWCNT bundle can be obtained assuming that CNT shells are parallel electrical conductors. On the other hand, SWCNT having only single shell its equivalent resistance  $R_{eqv}$  is  $R_k$  itself. Details of SWCNT modeling has been explained in our work reported in [49].

To estimate equivalent resistance of SWCNT bundle or MWCNT, one requires to have a knowledge of total number of CNT shells in that particular kind of CNT based interconnect. In case of MWCNT (Fig. 2.3), total number of shells,  $N_{shell}$ , can be obtained from Eq. (2.3) as follows,

$$N_{shell} = 1 + \left(\frac{D_{out} - D_{in}}{2\delta}\right) \tag{2.3}$$

where various parameters are described below,

$D_{out}$  = outer diameter of a MWCNT,

$D_{in}$  = inner diameter of a MWCNT and

$\delta$  = inter shell gap and equals to 0.34 nm.

In Fig. 2.3. MWCNT and its distribution of concentric shell is shown where MWCNT is lying on a ground plane. Here  $t_{ILD}$  is the thickness of interlayer dielectric. After obtaining the total number of shells in MWCNT, equivalent resistance of interconnect can be obtained. Since all these shells are contributing in transport with their average number of conducting channels regardless whether these are metallic or not; by combining them together will give the total contribution of all shells. Equivalent resistance can be then obtained from the following equation [51],

$$R_{eqv} = \left(\frac{1}{R_1} + \frac{1}{R_2} + \dots + \frac{1}{R_k} + \dots + \frac{1}{R_{N_{shell}}}\right)^{-1} + R_{contact}$$

$$= \frac{h}{2q^2} \left(\sum_{k=1}^{N_{shell}} \frac{M_k \lambda_{eff}(L, D_k, T_k, V)}{\lambda_{eff}(L, D_k, T_k, V) + L}\right)^{-1} + R_{contact}$$

(2.4)

In Eq. (2.4),  $R_{contact}$  is non-ideal resistance between CNT and metal. Contact resistance has been measured and is found varying widely because of contact metal, contact area, contact length and defects [52]. As reported contact resistance varies from few hundreds of ohms to several kilo-ohms [37, 53, 54]. In this study, an experimental value of  $1 \text{ k}\Omega/m^2$ [55] is used. It is obtained by calculating the annular contact region multiplied by  $1 \text{ k}\Omega/m^2$ .

Figure 2.3: Concentric circles showing MWCNT shells with the ground plane.

SWCNT bundle can be obtained by piling SWCNTs in different geometrical shapes. In this work, rectangular shape as shown in Fig 2.1 is considered. This is the most common interconnect geometry for VLSI technology. For SWCNT bundle, total number of CNT shells is different and can be obtained from the following equation:

$$N_w = Int\left\{\frac{W-D}{D+\delta}\right\} + 1 \tag{2.5}$$

$$N_H = Int \left\{ \frac{2(H-D)}{\sqrt{3(D+\delta)}} \right\} + 1$$

(2.6)

$$N_{shell} = N_W N_H - Int \left\{ \frac{N_H}{2} \right\} \tag{2.7}$$

where various parameters are explained as follows,

$N_w$  = number of CNT shells in the direction of width,

$N_H$  = number of CNT shells in the direction of Height,

D = diameter of CNT and

$\delta$  = inter shell gap and equals to 0.34 nm.

Function *Int* computes an integer value for everything enclosed in by curly brackets. Eq. (2.7) counts  $N_{shell}$  as the total number of SWCNT shells, which could fit for a rectangular cross-sectional geometry of SWCNT based interconnect. Once  $N_{shell}$  is available, Eq. (2.4) can be used to estimate the equivalent resistance of SWCNT bundle based interconnect. Again, for SWCNT,  $N_{shell}$  is 1.

#### **2.2.2.** Equivalent Inductance $(L_{eqv})$

After knowing equivalent resistance, it is important to estimate the inductance and capacitance of interconnect. For small device dimension besides classical electrostatic

capacitance, there is also quantum capacitance. For the same reasoning besides magneto-static inductance, there is also kinetic inductance. In this section, formulae for these both kinds of inductances associated with different kinds of CNT based interconnects is disucssed. Magnetic inductance,  $L_{MK}$ , which depends on the geometrical factor, can be obtained from Eq. (2.8) for a cylindrical conductor [27],

$$L_{Mk} = \frac{\mu}{2\pi} \ln(\frac{h_k}{2r_k}) \tag{2.8}$$

where various parameters are described as follows,

$h_k$  = distance between ground plane and the center of k<sup>th</sup> CNT shell,

$r_k$  = radius of CNT shell, and

$\mu$  = magnetic permeability of the CNT environment.

This magnetic inductance is quite important for SWCNT because of the small diameter. However, for a MWCNT with many concentric shells the magnetic inductance plays a lesser important role in overall inductance. Since diameters of outer shells are large, magnetic inductance becomes less significant for outer shells. Again, if one counts these in parallel to estimate overall inductance it will be less significant. Quantum inductance which comes in series with the magnetic inductance,  $L_K$ , can be estimated from the following equation [56],

$$L_K = \frac{\pi\hbar}{2q^2 v_F M_k} \tag{2.9}$$

Where  $v_F$  is Fermi velocity (8.854x10<sup>5</sup> ms<sup>-1</sup>) [42], and  $\hbar$  is reduced Planck constant. To obtain equivalent inductance, one requires adding right side of Eqs. (2.8) and (2.9) and then counting them in parallel as done in the case of equivalent resistance in Eq. (2.4). Calculations would be easier if one assumes that magnetic inductance is less significant in comparison to kinetic inductance. In case of SWCNT bundle, while taking all the shells into consideration, contribution from magnetic inductance will be divided by the total number of shells. In case of MWCNT, different shells correspond to different diameters. Shell diameters of a MWCNT increases from center to the surface. For increased diameter, magnetic component of inductance becomes less important as described in Eq. (2.8). For instance, for a MWCNT with 100 nm outer diameter, quantum inductance of innermost shell is 5.8188x10<sup>4</sup> times greater than the claimed magnetic inductance of that shell [51]. On the other hand, SWCNT with a diameter of ~1 nm and oxide thickness over which SWCNT is deposited is  $\sim 100$  Å, the calculated value of  $L_{\rm Mk} \sim 1$  pH/ $\mu$ m which is very small compared to the value of  $L_k$  which is in the range of nH/ $\mu$ m. With this argument, one can simplify the equivalent inductance though with some loss of accuracy and express by the following equation,

$$L_{eqv} = \frac{\pi \hbar}{2q^2 v_F \sum_{k=1}^{N_{shell}} M_k}$$

(2.10)

N<sub>shell</sub> can be calculated for MWCNT and for SWCNT bundles from Eqs. (2.3) and (2.7) respectively. In case of metallic SWCNT, total number of conducting channels are only 2. For SWCNT bundle and MWCNT based interconnect one needs to carry summation over all CNT shells to obtain total number of conducting channels. It is to be noted that total number of shell is

different than the total number of conducting channels. Number of shells is a physical quantity which counts the total number of SWCNT tubes fitted in to the interconnect geometry. On the other hand, number of conducting channels are electronic channels, which are coming from the band structure calculations. One CNT shell might have multiple electronic channels for transportation of electrons. Finally, for SWCNT bundle based interconnect assuming same diameters of all CNTs one can further simplify the equivalent inductance from Eqs. (2.2) and (2.10) as follows,

$$L_{eqv} = \frac{\pi \hbar}{2q^2 v_F \sum_{k=1}^{N_{shell}} M_k} = \frac{3\pi \hbar}{4q^2 v_F N_{shell}}$$

(2.11)

## **2.2.3.** Equivalent Capacitance $(C_{eqv})$

As for inductance, small dimensional interconnects have two kinds of capacitances. One is electrostatic in nature and depends on the geometric shape and dielectric constant of materials. The other one is quantum in nature. Electrostatic capacitance ( $C_{EK}$ ) of a CNT is similar to a cylindrical conductor and can be estimated as follows,

$$C_{Ek} = \frac{2\pi\varepsilon}{\ln\frac{h_k}{2r_k}} \tag{2.12}$$

where,  $\varepsilon$  is dielectric permittivity,  $h_k$  is distance between ground plane and the center of  $k^{th}$  CNT shell and  $r_k$  is radius of CNT shell. Quantum capacitance is in series with this electrostatic capacitance and can be estimated from the following equation [3],

$$C_{\mathcal{Q}} = \frac{2q^2}{hv_F} M_k \quad . \tag{2.13}$$

For metallic SWCNT  $M_k$  is 2. Usually, everyone wants a material with low dielectric constant as an ILD to surround the interconnect into. Since electrostatic and quantum capacitances are in series, the one lower in value will dominate in estimation of overall capacitance. If the dielectric constant is low and the distance of interconnect layer from the ground plane is high electrostatic capacitance will dominate over the quantum capacitance. Actually, there is no general rule to find out which one will dominate over the other one. Therefore, for detail calculations one always requires to include both of them to estimate equivalent capacitance numerically. However, to express analytically one can make simplified assumptions. Electrostatic capacitance is dominant over quantum capacitance only for MWCNT with fewer shells. For a MWCNT with more shells quantum capacitance is approximately thousand times more than the electrostatic capacitance of the outer shell [51]. Hence, in calculation of equivalent capacitance considering only quantum capacitance is a good approximation. Considering only quantum capacitance, equivalent capacitance can be then estimated from the following equation,

$$C_{eqv} = \frac{2q^2}{hv_F} \sum_{k}^{N_{shell}} M_k \tag{2.14}$$

For SWCNT bundle, it can be further approximated using Eq. (2.15) as follows,

$$C_{eqv} = \frac{2q^2}{hv_F} \sum_{k}^{N_{shell}} M_k = \frac{4q^2 N_{shell}}{3hv_F}$$

(2.15)

### **2.2.4.** Effective Mean Free Path $(\lambda_{eff})$

One of the most important parameter in electronic transport properties is the carrier mean free path (MFP). In CNT, electrons are the major charge carriers. Electrons in a CNT go through many different collisions. In this section, different mean free paths associated with different collisions are calculated and finally Matthiessen's rule is to be used to estimate effective MFP,  $\lambda_{eff}$ , of an electron. Phonons are quantized lattice atom vibrations. Due to vibrations, positive ions of atoms are displaced from their equilibrium positions and this changes the potential profile in the atomic scale. This change in potential is the cause for delocalized electrons to get scattered. Optical phonons and acoustic phonons interact with mobile electrons and thus scatter electrons. Even without any biasing, electrons spontaneously get scattered with the optical and acoustic phonons. Scattering lengths of electrons due to acoustic ( $\lambda_{ac}$ ) and optical phonons ( $\lambda_{op}$ ) can be estimated from the following equations [57],

$$\lambda_{ac} = \frac{400.46 \times 10^3 D}{T} \tag{2.16}$$

$$\lambda_{op} = 56.4D \tag{2.17}$$

In Eqs. (2.16) and (2.17), D is the diameter of a SWCNT and T is the temperature of a particular shell. The increase in temperature increases the population of acoustic phonons, which eventually increases the collision rate. Hence, an increase in temperature decreases the scattering length of electrons. The scattering length,  $\lambda_{ac}$  contributes directly to MFP. However  $\lambda_{op}$ , which is only

dependent on the diameter, needs to be modified with temperature dependence as in Eq. (2.18). An electron can get scattered by absorbing or emitting an optical phonon. The scattering length due to optical phonon absorption,  $\lambda_{op,abs}$ , has been modeled by the following equation [37],

$$\lambda_{op,abs} = \lambda_{op} \frac{N_{op}(300) + 1}{N_{op}(T)}$$

(2.18)

In Eq. (2.18),  $\lambda_{op}$  can be obtained from Eq. (2.17).  $N_{op}$  in the following describes the optical phonon occupation, which is the Bose-Einstein statistics and given by,

$$N_{op} = \frac{1}{\exp(h\omega_{op}/K_BT) - 1} \tag{2.19}$$

In Eq. (2.19),  $\omega_{op}$  is the optical phonon frequency and its typical energy value varies from 0.16 eV to 0.20 eV. For numerical calculations, this value is taken as 0.16 eV. From Eq. (2.19), it is obvious that as the temperature increases,  $N_{op}$  increases. Consequently, if  $N_{op}$  increases, scattering length due to optical phonon absorption ( $\lambda_{op,abs}$ ) decreases according to Eq. (2.18). Therefore, at a high temperature or high bias, an electron suffers more scatterings due to optical phonon absorption. Electrons also get scattered due to the emission of optical phonons. Optical phonon emission process has two components. One is due to the absorbed energy. The other component is due to the electric field induced by the bias across the SWCNT length. Both of these components can be estimated as follows:

$$\lambda_{op,ems}^{abs} = \lambda_{op,abs} + \lambda_{op} \frac{N_{op}(300) + 1}{N_{op}(T) + 1}.$$

(2.20)

$$\lambda_{op,ems}^{fld} = \frac{h\omega_{op} - K_B T}{qV/L} + \lambda_{op} \frac{N_{op}(300) + 1}{N_{op}(T) + 1}.$$

(2.21)

In Eqs. (2.20) and (2.21), q is electronic charge, V is the bias voltage across the CNT and L is the length. From Matthiessen's rule, one can estimate the MFP due to these aformentioned scattering processes and is expressed as follows,

$$\frac{1}{\lambda_{op,ems}} = \frac{1}{\lambda_{op,ems}^{abs}} + \frac{1}{\lambda_{op,ems}^{fld}}.$$

(2.22)

Eq. (2.22) estimates the effective MFP only due to the optical phonon emission. Following equation can be used to estimate overall MFP of electrons.

$$\frac{1}{\lambda_{eff}} = \frac{1}{\lambda_{ac}} + \frac{1}{\lambda_{op,ems}} + \frac{1}{\lambda_{op,abs}}$$

(2.23)

Near charge neutrality point, electron-electron scattering mean free path is on the order of several micrometers and it is observed experimentally [58]. Because of the large mean free path, electron-electron interaction is not a dominant scattering event to consider in Eq. (2.23) while electron-phonon scatterings are the dominant events [59]. Eq. (2.23) serves as a quick estimation of effective MFP of an electron. The effective MFP ( $\lambda_{eff}$ ) can be used in Eq. (2.4) to estimate the temperature and geometry dependent equivalent resistance of CNT interconnects.

## 2.2.5. Equivalent Circuit

Once the equivalent resistance is obtained, inductance and capacitance of a CNT interconnect, one can model its equivalent circuit. Yao et al. [41] and D'Amore et al. [60] have

showed how to model equivalent circuit for MWCNTs . SWCNT bundle has been modeled by Sarto et al. [61]. These models mostly involved RLC parameters of multiple lines and coupling impedance in between lines. In inductance and capacitance, they considered both the classical and quantum counterparts. However, it is required to have a single conductor transmission line model to describe the electrical performances in a way that is more compact. It is to be noted that compact modeling can help to simulate a large system with limited computing resource. Sarto et al. [42] proposed single conductor transmission line model for the MWCNT which can be modified for any kind of CNT. Following this one can have a single conductor transmission line model for any kind of CNT as described here. Only the equivalent R, L and C values will be different depending on which kind of CNT interconnect needs to be modeled. For high frequency characterization of interconnect, this transmission line model will be very useful. In scattering parameter calculations, this equivalent single conductor model has been used along with per unit length circuit parameters. Equivalent circuit is as shown in Fig. 2.4.

### 2.3. Thermal Properties

Now it is important to know thermal properties and to study how these affect electronic transport. The motivation of this chapter is to examine how Joule heating limits electronic transport through CNT VLSI interconnects. Therefore, it is important to analyze different CNT variants in terms of thermal stability. The fundamental approach is to model temperature distribution and to study thermal stability of interconnect. Phenomenological heat diffusion equation can be used as long as the length of CNT is long enough in comparison to the mean free path of a phonon. If the CNT length becomes comparable to the phonon mean free path necessary

physics cannot be described by the phenomenological Fourier heat equation. In the latter case, one needs to solve the Boltzmann transport equation (BTE) for phonons which is less intuitive and computationally more expensive. Again, standard BTE has its own limitations of treating phonon as a classical particle instead of the quantum nature of phonon. Cahill et al. [62, 63] have reviewed the recent progress of thermal transport in the nanoscale dimension. In most of the practical cases, CNT lengths are in the order of a few micrometers whereas phonon effective MFP is in the order of a few hundreds of nanometers. Therefore, it is permissible to use Fourier heat equation with necessary boundary and initial conditions. In this section, different variants of Fourier heat equation are described with their boundary conditions for different kinds of CNT interconnects. Since MWCNT and SWCNT bundle consists of SWCNT in different geometric orientations it is natural to study the thermal properties of SWCNT based interconnect first and then other variants of CNT.

# 2.3.1. Thermal Properties of SWCNT

SWCNT is a quasi-one-dimensional and does not have enough surface area and cross-sectional area to dissipate heat. Hence it is prone to thermal break down more than any other variants of CNT. Even though SWCNT is highly heat conductive, it has been observed experimentally that the conducting carbon nanotube breaks down due to Joule heating and thus limits its current density [64, 65]. Thermal break down of SWCNT has been studied by Pop et al. [37]. Huang et al. [66] have studied thermal transport and observed experimentally that the hottest

Figure 2.4: Single conductor transmission line model of CNT interconnect.

spot is located at the center of the tube from where breakdown is initiated. Geometry of SWCNT is essentially a single one-dimensional wire. Therefore, the Fourier heat equation can be described by one-dimensional equation.

$$\frac{\partial}{\partial z} \left( A \kappa \frac{\partial T}{\partial z} \right) + p = A \rho c \frac{\partial T}{\partial t}$$

(2.24)

In Eq. (2.24),  $\kappa$  is the heat conductivity, A is the cross-sectional area ( $D\pi\delta$ ), t is time, T is the temperature at a given point of SWCNT, p is Joule heating source power per unit length, c is specific heat of CNT and  $\rho$  is density of CNT. A typical diameter of SWCNT is 1 nm and thickness is 0.34 nm which is the interlayer distance in graphite. Under the assumption of uniform heating, uniform cross sectional area of CNT, steady state solution can be obtained using the work of Pop et al. [37],

$$A\frac{\partial}{\partial z} \left( \kappa \frac{\partial T}{\partial z} \right) + p - g \left( T - T' \right) = 0$$

(2.25)

where T' is the substrate temperature, g is the measure of heat conductivity of CNT through substrate. The higher value of g implies that CNT will be more thermally stable. Right hand side of Eq. (2.25) equals zero since a steady state solution is preferred. Being a one-dimensional problem, only one boundary condition is required to solve this problem. Typical substrate temperature is  $60^{\circ}$ ~70°C. Again, g depends on the interface of CNT and substrate and can either be measured experimentally or can be estimated from extensive first principle calculations. Pop et al. [37] measured the value of g associated with silicon substrate and found its value to be 0.15

Wm<sup>-1</sup>K<sup>-1</sup>. Thermal conductivity ( $\kappa$ ) is the most disputed parameter for CNT. It ranges from few hundreds to few thousands of Wm<sup>-1</sup>K<sup>-1</sup>. In the work of Yamada et al. [45] and Kitsuki et al. [46] thermal transport has been studied considering the thermal conductivity of CNT as constant. However, studies in [37, 40, 53, 67-69] have shown that the thermal conductivity is temperature dependent. This is why one needs to check with the most recent agreed experimental values for thermal conductivity until an established theoretical and experimental value has been obtained. For a constant value for thermal conductivity ( $\kappa$ ) a compact analytical solution has been shown in [37] as follows:

$$T(z) = T' + \frac{p}{g} \left[ 1 - \frac{\cosh\left(\frac{z}{\sqrt{\kappa Ag}}\right)}{\cosh\left(\frac{L}{2\sqrt{\kappa Ag}}\right)} \right]. \tag{2.26}$$

One of the important outcomes of Pop's study [37] is defining thermal healing length as follows:

$$L_{H} = \sqrt{\kappa A g} \ . \tag{2.27}$$

If the length of CNT is very large in comparison to the thermal heating length ( $L_H$ ) most of the heat will be lost by the substrate. On the other hand, if the length is comparable to  $L_H$  most of the heat diffuses through the contacts. In Eq. (2.26), p/g determines the peak temperature of the hottest spot which is the midpoint (z=0) temperature of SWCNT. Now from Eq. (2.26), one can find the temperature distribution for a given Joule heating (p) per unit length which is  $I^2R$  per unit length. Therefore, Eq. (2.26) is resistance (R) dependent. Again from Eq. (2.4) one knows that R is T dependent. Hence, there is a nonlinear relationship between R and T. This nonlinear relationship

can be taken into account by the iterative scheme, which is discussed in Section 2.3.4. Once T and R can be calculated from the coupled electro-thermal equations, thermal stability can be determined. If the temperature at any point of a SWCNT goes above the breakdown temperature 873 K, it melts down at that point and breaks the circuit. Since peak temperature is being determined by p (= $I^2R$ ), thermal stability depends directly on the bias current. This is how the Joule heating limits the current density and in worst case scenario, causes thermal breakdown of interconnects. For a 3  $\mu$ m long SWCNT and 2 nm diameter, maximum current has been calculated to be 20  $\mu$ A [37, 65]. Since longer SWCNT has more contacts with substrate it can dissipate heat quicker than the shorter one. Hence a length dependence of thermal stability comes into the picture. In our previous work reported in [49], length dependence of resistance has been presented as shown in Fig. 2.5. To summarize, length, diameter, temperature and bias voltage or bias current decide the mean free path and resistance of CNT interconnect. Resistance and temperature are intertwined and needs to be solved with iterative scheme described in Section 2.3.4.

## 2.3.2. Thermal Properties of SWCNT Bundle

Heat equation for SWCNT bundle is a three-dimensional problem to be solved with necessary boundary conditions. If the cross-sectional area is very small and the length is very large, one can assume it as a one-dimensional problem. For one-dimensional case, the solution of heat equation is already discussed in previous section. However, in case of local interconnect the cross-section is large enough and interconnect is not comparatively long enough to assume one-dimensional problem. Hayashi et al. [70] noted that there is anisotropy of heat conductivity in MWCNT. This anisotropy suggests that heat conductivity is very high in axial direction in comparison to the radial direction. Since MWCNT and SWCNT bundle only vary in placement

of SWCNT shell in different geometric orientation; similar anisotropy is also possible for SWCNT bundle. Heat conductivity will be always dominant in axial direction while electron and phonon transport is happening in the shell. In contrast whenever transport involves with an adjacent shell, heat carriers need to face the inter-shell thermal resistance. Hence heat conductivity will not be high in the radial direction. Therefore, in cross-section of SWCNT based interconnect temperature gradient will be observed. There will be a temperature distribution in the cross-section of SWCNT bundle based interconnect due to this anisotropy of heat conductivity. A cross sectional distribution of temperature means different SWCNT wires will be at different temperatures causing different temperature dependent resistance ( $R_k$ ). Thus, a three-dimensional heat equation is to be solved as follows:

$$\frac{\partial}{\partial x} \left( A \kappa_x \frac{\partial T}{\partial x} \right) + \frac{\partial}{\partial y} \left( A \kappa_y \frac{\partial T}{\partial y} \right) + \frac{\partial}{\partial z} \left( A \kappa_z \frac{\partial T}{\partial z} \right) + p - g \left( T - T' \right) = A \rho c \frac{\partial T}{\partial t}. \tag{2.28}$$

Where,  $\kappa_x$ ,  $\kappa_y$ , and  $\kappa_z$  is heat conductivity in x,y and z directions. The geometry of SWCNT bundle based interconnect is a three-dimensional rectangular bar,  $p = (l^2 R_{eqv})/(WxLxH)$ , where W, L, and H are width, length and height of interconnect. Substrate temperature T' can be taken as 300 K and will serve as a boundary condition for solving Eq. (2.28). Definition of other parameters are given in the previous section. Under the following assumption, one can simplify Eq. (2.28) to solve this problem analytically or numerically. Following assumptions are made:

- 1. Heat generation is uniform throughout the whole interconnect

- 2. Cross-section of interconnect is uniform

Figure 2.5: Length dependence resistance of SWCNT interconnect.

- Anisotropy of heat conductivity is only two-dimensional: radial and axial direction of a CNT

- 4. Steady state solution

- 5. Interconnect length is short enough so there will be no temperature variation along the length (z-axis)

Considering above-mentioned assumptions, following equation is to be solved:

$$\kappa_{x} \frac{\partial^{2} T}{\partial x^{2}} + \kappa_{y} \frac{\partial^{2} T}{\partial y^{2}} + p - g \left( T - T' \right) = 0.$$

(2.29)

In Eq. (2.29), constant cross-sectional area (A) can be absorbed into other constants. Heat conductivity through substrate (g) is yet to be measured experimentally for SWCNT bundle based interconnect. Although heat generation might not be uniform in real experiments we assumed it for the simplicity of modeling.

## 2.3.3. Thermal Properties of MWCNT

Three-dimensional MWCNT is inherently more stable than SWCNT in terms of thermal stability. On top of thermal stability, growth techniques of MWCNT are easier than SWCNT. This is why MWCNT is preferred over SWCNT as the VLSI interconnect. For better understanding the performances of various CNT interconnects and to compare them it is essential to study MWCNT interconnect as well. Temperature distribution along the MWCNT considering Joule heating has been reported by Feng et al. [71] and later they studied the cross-talk effects for the VLSI interconnect [72].